Sister Conferences

|

Advanced Program (New!(as of 3 Apr 2009))

Keynote Presentation

| "Future Robotics and the Key Components" |

|

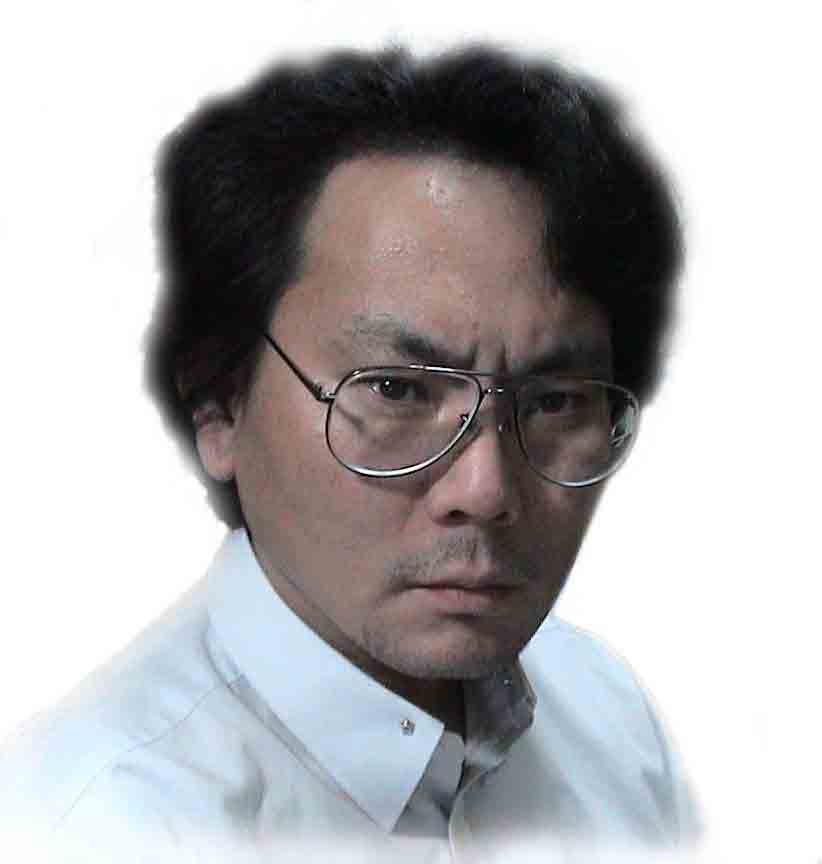

| Hiroshi Ishiguro |

Department of Adaptive Machine Systems, Osaka University

ATR Intelligent Robots and Communication Laboratories |

Abstract:

Many robotics researchers are exploring new possibilities of intelligent robots in our everyday life. Humanoid and androids, which have various modalities, interact and communicate with humans as new information media for providing various daily services. This talk introduces a series of robots developed in ATR Intelligent Robotics and Communications Laboratories and Department of Adaptive Machine Systems, Osaka University and discusses the fundamental issues. One of the fundamental issues is the hardware development. The reliable and low cost robots expected to work in our future society requires various computer chips for handling sensory information and controls the behaviors. This talk also discusses what kinds of chips are expected for developing the future robots that works in our town and home.

|

| "Cisco QFP - Quantum Flow Processor -" |

|

| Will Eartherton |

| Cisco Systems inc, ERBU Director Engineering |

Abstract:

Cisco has seen a growing need for Service Providers to handle the growing amount of traffic and complexity of network traffic then decided to create its own networking chipset called "Cisco QFP - Quantum Flow Processor". Cisco QFP is the most advanced networking silicon and the first fully integrated programmable networking chipset which consists of 40 cores, has 800 million transistor density and can perform up to 160 simultaneous processes. Cisco QFP is powering the date plane engine of Cisco ASR1000 Series Aggregation Service Router which is suitable at network edge for IP NGN and Enterprise Network with its high performance, versatile functionality, high availability, less space and power efficiency. In this keynote, Cisco QFP architecture and its applications are introduced.

|

| "New 3-D Integration Technology and 3-D Systems " |

|

| Mitsumasa Koyanagi |

Department of Bioengineering and Robotics

Tohoku University |

Abstract:

A three-dimensional (3-D) integration technology based on the wafer-to-wafer bonding using Through-Silicon Vias (TSV's) has been developed. A 3-D image sensor chip, 3-D shared memory chip, 3-D artificial retina chip and 3-D microprocessor test chip have been fabricated by using this technology. In the wafer-to-wafer 3-D integration technology, however, the overall chip yield exponentially decreases with an increase in the number of stacked layers. To solve these problems, we have proposed a new 3-D integration technology called super-chip integration in which more than one thousand of known good dies (KGD's) are simultaneously aligned and bonded onto chips on a wafer using a self-assembly technique.

|

Invited Session

| "STP Engine, a C-based Programmable HW Core featuring Massively Paralleland Reconfigurable PE Array: its Architecture, Tool, and SystemImplications" |

|

| Masato Motomura |

| 1st SOC Operations Unit, NEC Electronics |

Abstract:

Stream Transpose (STP) Engine is a programmable HW core to accelerate stream processing in modern system LSIs. It is composed of an array of numerous numbers of processing and memory elements as well as an intelligent data streaming HW mechanism. Key differentiation from other many-core type parallel architectures lies in its programming model: i.e., a design tool based on high-level HW synthesis technology compiles a C source code into a set of pseudo HW configurations which are spatially mapped onto the array. The STP engine is productized in 90nm-generation system LSIs, and is targeted for wider-range use in forthcoming generations beyond 40nm. This talk covers the core's architecture and tool issues, as well as its real world system applications.

|

Special Session

| "Designing Cool Chips Using 3D Stacking Technology" |

|

| Yuan Xie |

| Pennsylvania State University |

Abstract:

As technology scales, interconnects have become a major performance bottleneck and a major source of power consumption for nanoscale VLSI chips. One promising option is 3D architectures where a stack of multiple device layers, with Through-Silicon-Vias (TSVs) going through them, are put together on the same chip. As fabrication of 3D integrated circuits has become viable, developing CAD tools and circuit/architectural techniques areimperative to explore the design space for 3D IC design. In this tutorial, a brief introduction on 3D IC integration technology will be given, and the challenges of EDAdesign tools that can enable the adoption of 3D ICs will be discussed, and the microarchitecture potentials of using3D technology will be introduced.

|

"Low power techniques for reconfigurable devices

focusing on dynamically reconfigurable processors" |

|

| Hideharu Amano |

| Dept. of ICS, Keio University |

Abstract:

Reconfigurable devices have been widely utilized in embedded systems whose power consumption is essential. Since traditional FPGAs require large power consumption compared with fixed hard-wired logic, it is a main problem for using embedded application. In order to cope with this problem, various types of techniques to reduce the dynamic and leakage power of FPGAs have been proposed. On the contrary, the dynamically reconfigurable processors achieve 8-10 times lower energy computation compared with DSPs with corresponding technologies, and it is the main motivationto be used in consumer products.

In this session, first, the power of both FPGAs and dynamically reconfigurable processors are analyzed, and the difference caused by their architectures is discussed. Then, various power reduction methods including operand isolation, reducing dynamic reconfiguration, controlling Vdd, dual Vdd, dual Vth and power gating are reviewed, and application to reconfigurable devices is discussed.

|

|

|

| |